We have extensive experience in developing accelerators using PCI Express IP. We are also familiar with technologies such as virtualization support and cache coherent protocols, and can assist in the design of FPGA logic and driver software to utilize these technologies.

Accelerator development using PCI-express IP

FPGA cards with interfaces such as QSFP28 are added on to the server to offload the processing of incoming and outgoing packets using custom logic. Various packet processing can be performed on demand, including DDoS filters, IP filters, protocol filters, security filters using DPI (Deep Packet Inspection), protocol conversion, transcoding, encapsulation, etc. Basically, throughput of 100 Gbps per engine can be achieved. In addition, since the FPGA can be treated as a NIC by the host application, it is possible to link conventional applications with the FPGA’s high-speed packet processing.

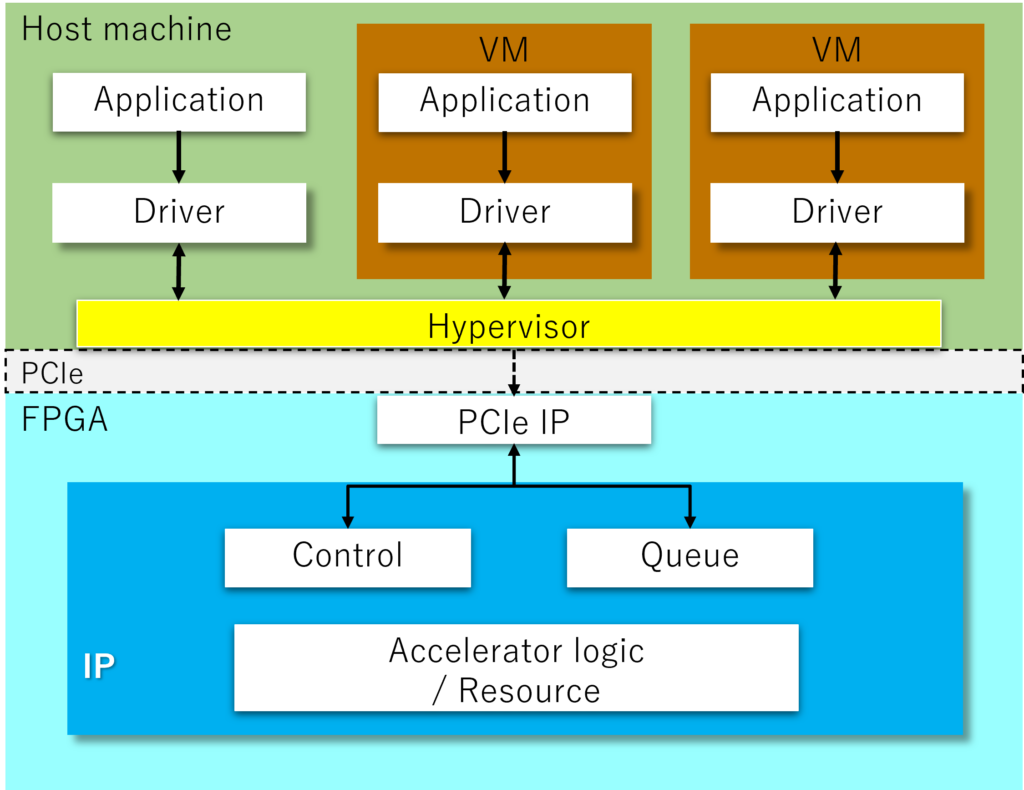

Support for Virtual Machine

By processing hardware packet processing outside the terminal in the form of a middlebox, the load on software processing at the terminal is not increased, preventing performance degradation and resource depletion. In addition, due to the inherent characteristics of hardware processing, many of the memory resource and vulnerability attacks that are problematic with software network stacks can be disabled, increasing security.

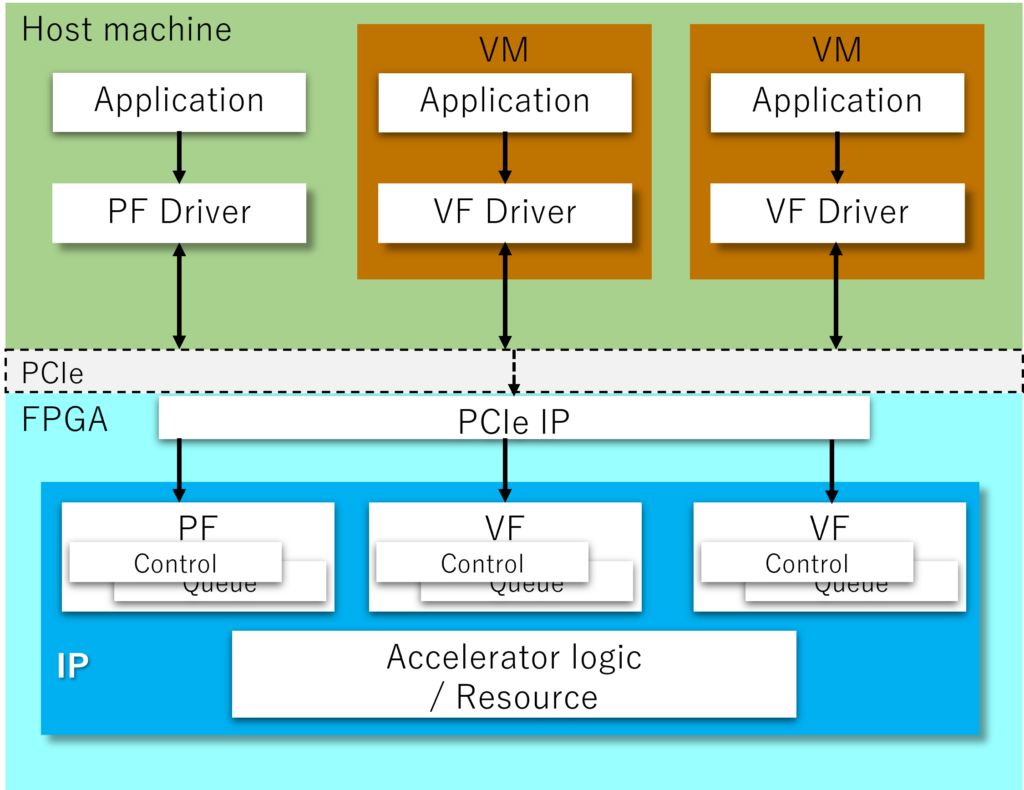

SR-IOV

Using the SR-IOV (Single Root-IO Virtualization) method, a feature of PCI express, it is possible to control devices directly from drivers of different VMs. The FPGA side can then provide separate control registers and command queues so that the Hypervisor does not become a bottleneck and can achieve the same performance as when used from a physical machine.

We support virtual machine environment by leveraging our expertise in high-performance logic and driver development for SR-IOV, including DMA and IOMMU.