PTU is a hard-wired network accelerator IP core that runs on FPGA or ASIC.

Equipped with a protocol termination function and a relay function, it is possible to realize a Smart NIC that meets customer needs.

Protocols such as ARP, IP, ICMP, UDP, TCP, TLS and flow control can be offloaded to the PTU, so the CPU only triggers the sending and receiving of data.

The system provides high throughput, low latency, and high security network processing.

It is also possible to realize all specific protocol processing with only PTU without CPU.

The TCP/IP-only offload IP core is known as the TCP Offload Engine (ToE), but PTU can also offload protocols above TCP.

* PTU : Protocol Termination Unit

Intellectual Highway’s TCP offload engine offloads full functionality and offers high quality, high reliability, high performance, and multi-session features that are applicable from the Internet to the data center.

By adding SSL/TLS extensions to our TCP offload engine, it is possible to handle SSL/TLS encryption processing of large numbers of sessions with high speed and low latency, which is very demanding on the CPU.

This can be applied to load balancers with SSL/TLS termination, etc., and since the CPU can concentrate on application processing, it can handle a large number of sessions very efficiently.

Features of Network Accelerator IP

-

High performance

Since IP / TCP / TLS is implemented in hard-wired, high throughput and low latency network processing is possible.

-

Robust security

Processes high-strength cryptographic algorithms at high speed. You don't have to worry about being attacked by open vulnerabilities like OSS.

-

Customize in a short period of time

We will develop additional protocol processing that meets customer needs in a short period of time.

High-performance network processing and robust security

In the 5G era, the number of computers connected to the network and the amount of data flowing will be enormous. At the same time, more computers are at risk of cyber attacks. Therefore, it is essential to achieve both higher performance network processing and robust security.

Network Accelerator IP developed by Intellectual Highway provides high-performance network processing and robust security compared to software processing.

Applications

High-performance video processing

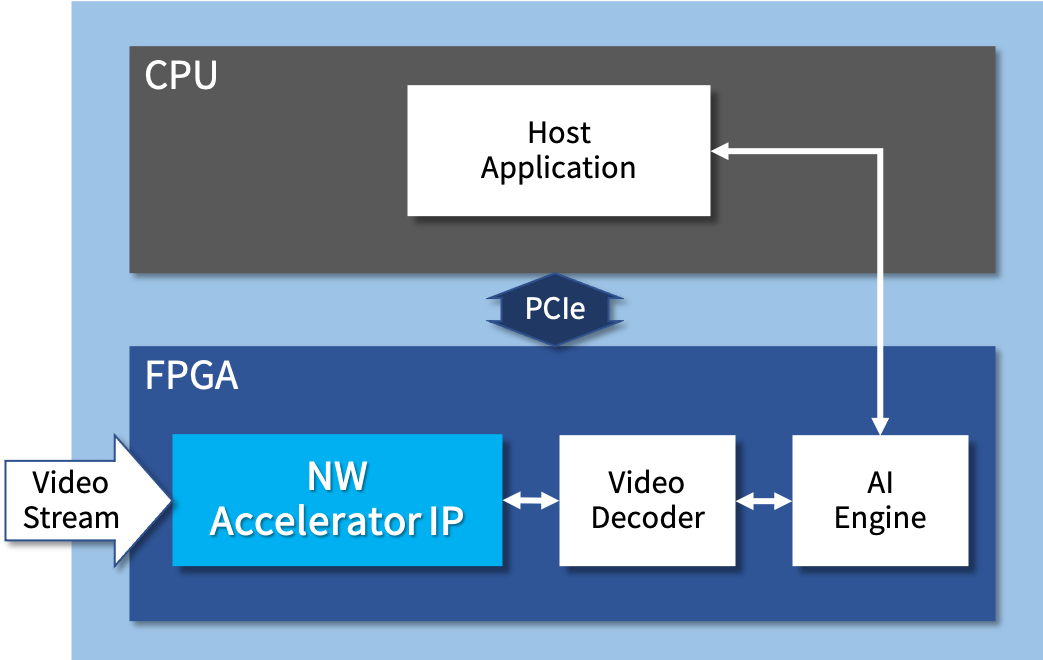

By integrating the network accelerator IP, hardware video decoder, and AI recognition engine, it is possible to recognize and process the input video from the network camera at high speed and with low latency without CPU processing.

It can be applied to real-time video analysis of in-vehicle cameras and surveillance cameras.

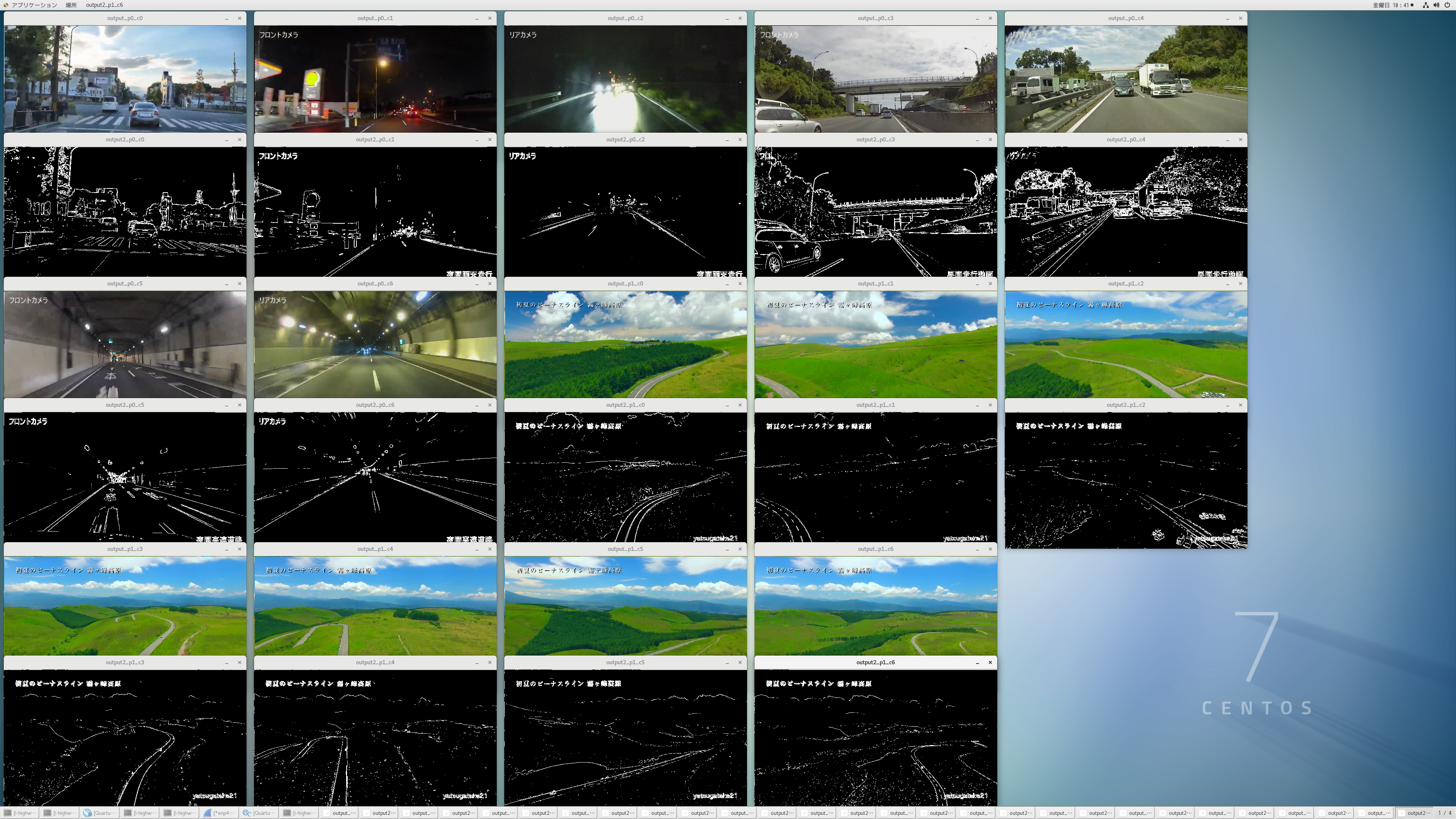

This is an example of simultaneously receiving 14 channels of HD resolution video from the network and applying median processing and edge extraction to the decoded image on the FPGA (Intel PAC Arria-10).

It is difficult for the CPU to handle such images at the same time, and it cannot be processed in real time.

Here, median and edge extraction are performed as an example, but any image processing can be implemented. It is also possible to write image processing algorithms in C language and develop and integrate image processing in a short period of time using high-level synthesis.

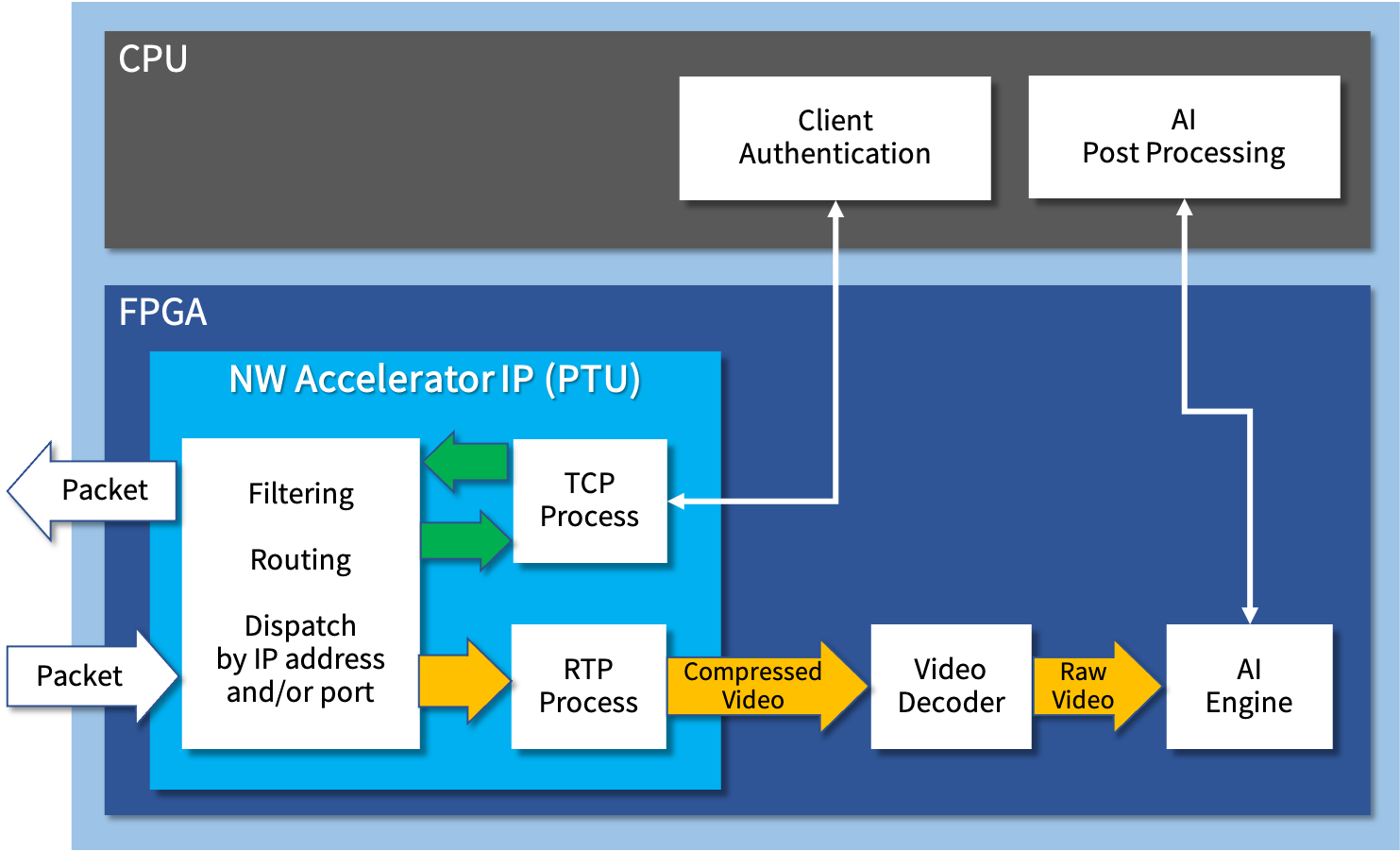

Hybrid processing by software and hardware

Since PTU can freely set the distribution for multi-protocol, the hardware performs high-load video processing that requires real-time performance such as decoding and recognition processing, and software can handle real-time unnecessary processing such as client authentication.