Using a hardware high-speed, low-latency packet processing engine, additional delay can be removed. Packet forwarding, packet rewriting, encapsulation/decapsulation, encryption/decryption, and load balancing can be realized.

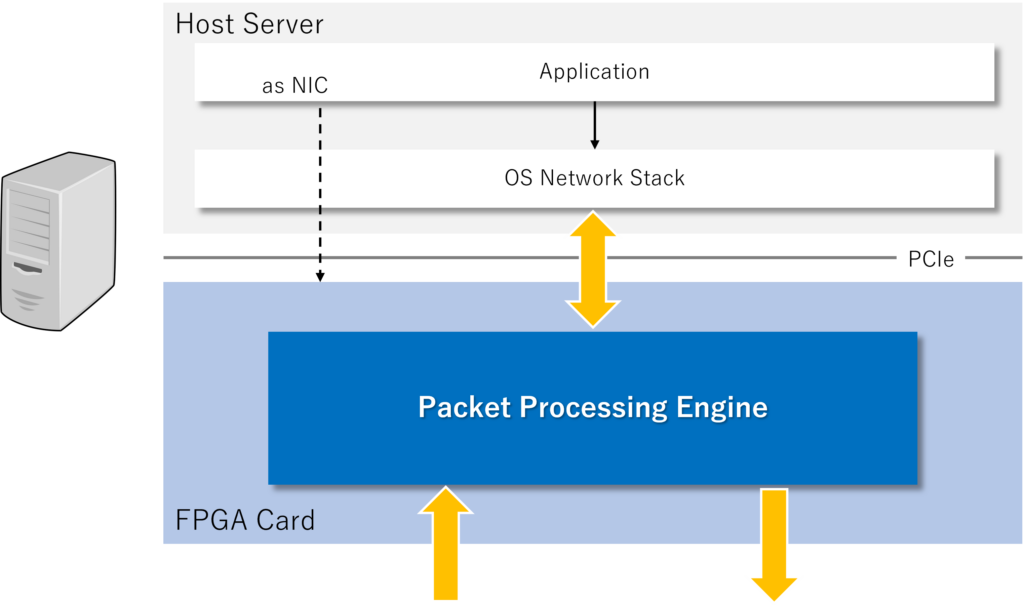

Offloading packet processing of servers

FPGA cards with interfaces such as QSFP28 are added on to the server to offload the processing of incoming and outgoing packets using custom logic.

Various packet processing can be performed on demand, including DDoS filters, IP filters, protocol filters, security filters using DPI (Deep Packet Inspection), protocol conversion, transcoding, encapsulation, etc. Basically, throughput of 100 Gbps per engine can be achieved. In addition, since the FPGA can be treated as a NIC by the host application, it is possible to link conventional applications with the FPGA’s high-speed packet processing.

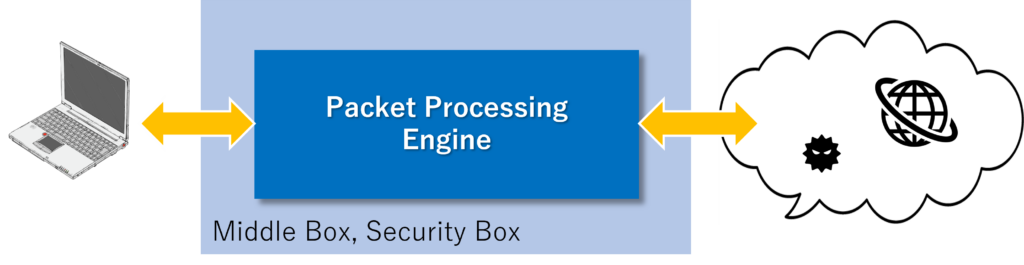

Middle Box / Security Box for IoT devices

By processing hardware packet processing outside the terminal in the form of a middlebox, the load on software processing at the terminal is not increased, preventing performance degradation and resource depletion.

In addition, due to the inherent characteristics of hardware processing, many of the memory resource and vulnerability attacks that are problematic with software network stacks can be disabled, increasing security.