RDMA (RoCEv2) IP

RDMA is a mechanism where hardware directly writes to and reads from the main memory, resulting in minimal CPU load and minimal OS intervention, enabling high-speed, low-latency data transfer. RoCEv2 is currently mainstream RDMA protocol which uses Ethernet as its physical layer and operates over UDP. In addition to standard RDMA IP for DRAM-based DMA, we also provide specialized RDMA IP which is tailored for embedded system as an I/O nodes .

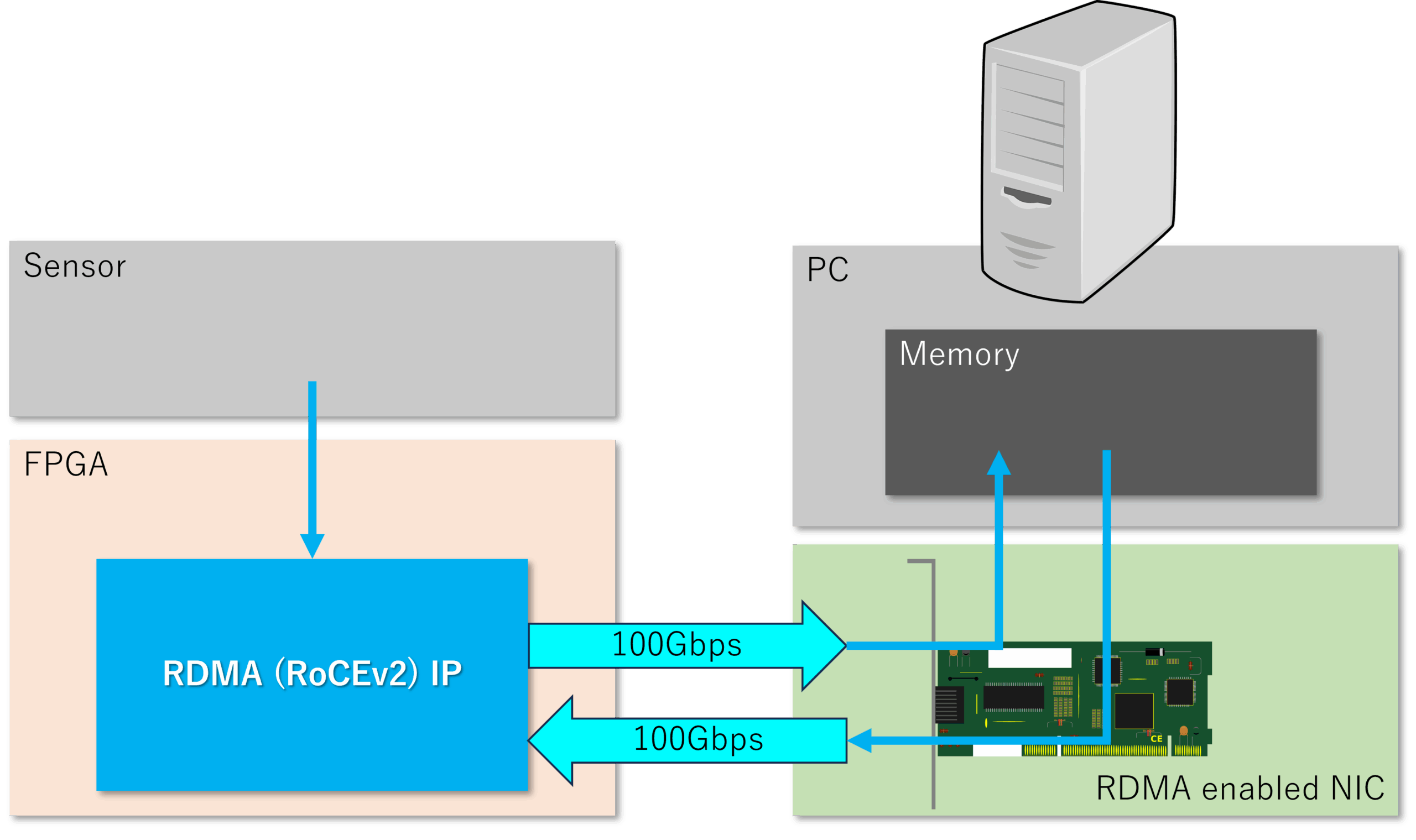

RDMA IP for I/O Nodes

Our RDMA IP for I/O nodes is an IP that enables transfers outputs from sensors and other devices using the RDMA (RoCEv2) protocol entirely without CPU involvement. By carrying data on the RDMA protocol, data can be sent and received without placing load on the CPU of the connected PC. This enables the systems for collecting high-bandwidth sensor data and transferring video data with low latency.

Applications include testing equipments, video streaming, and data movement between accelerators in HPC (High-Performance Computing) systems.

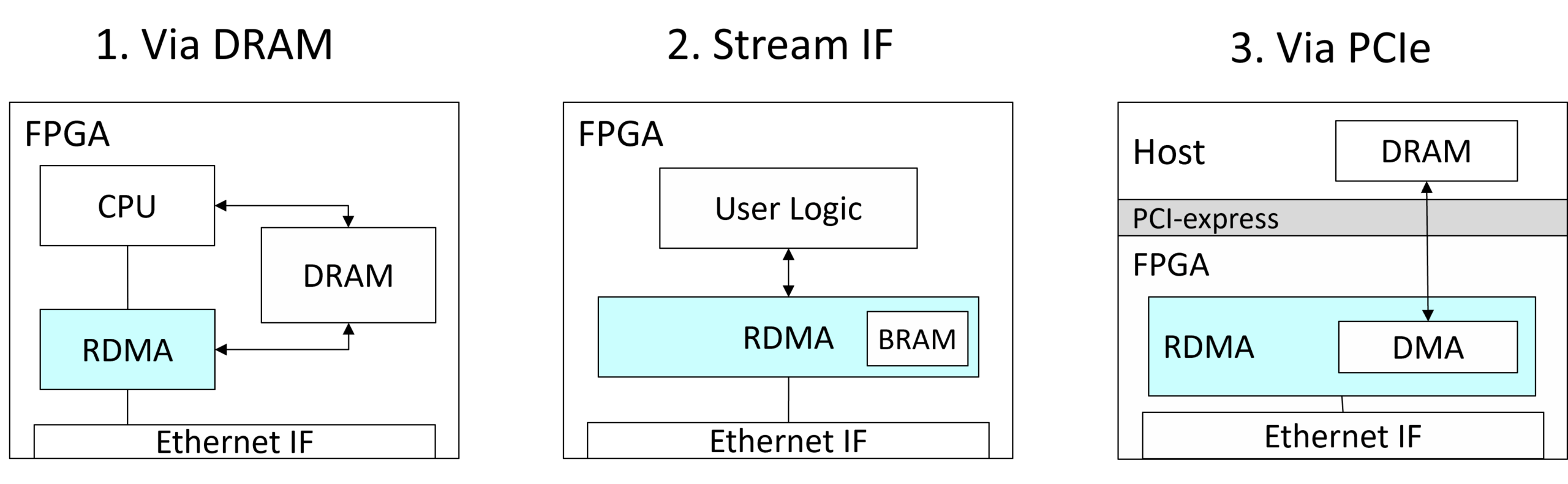

The types of API

Three different types of interfaces.

The DRAM-based interface achieves RDMA by placing all target data onto DRAM connected via bus to the FPGA and issuing commands to the IP.

The stream interface is suitable for directly inputting data from sensors and other sources into the IP, and can be implemented without DRAM.

The interface via descriptors operates on an FPGA connected to the host via PCI Express. The host controls it using descriptors, and data transfer is performed via the FPGA’s DMA without CPU overhead.

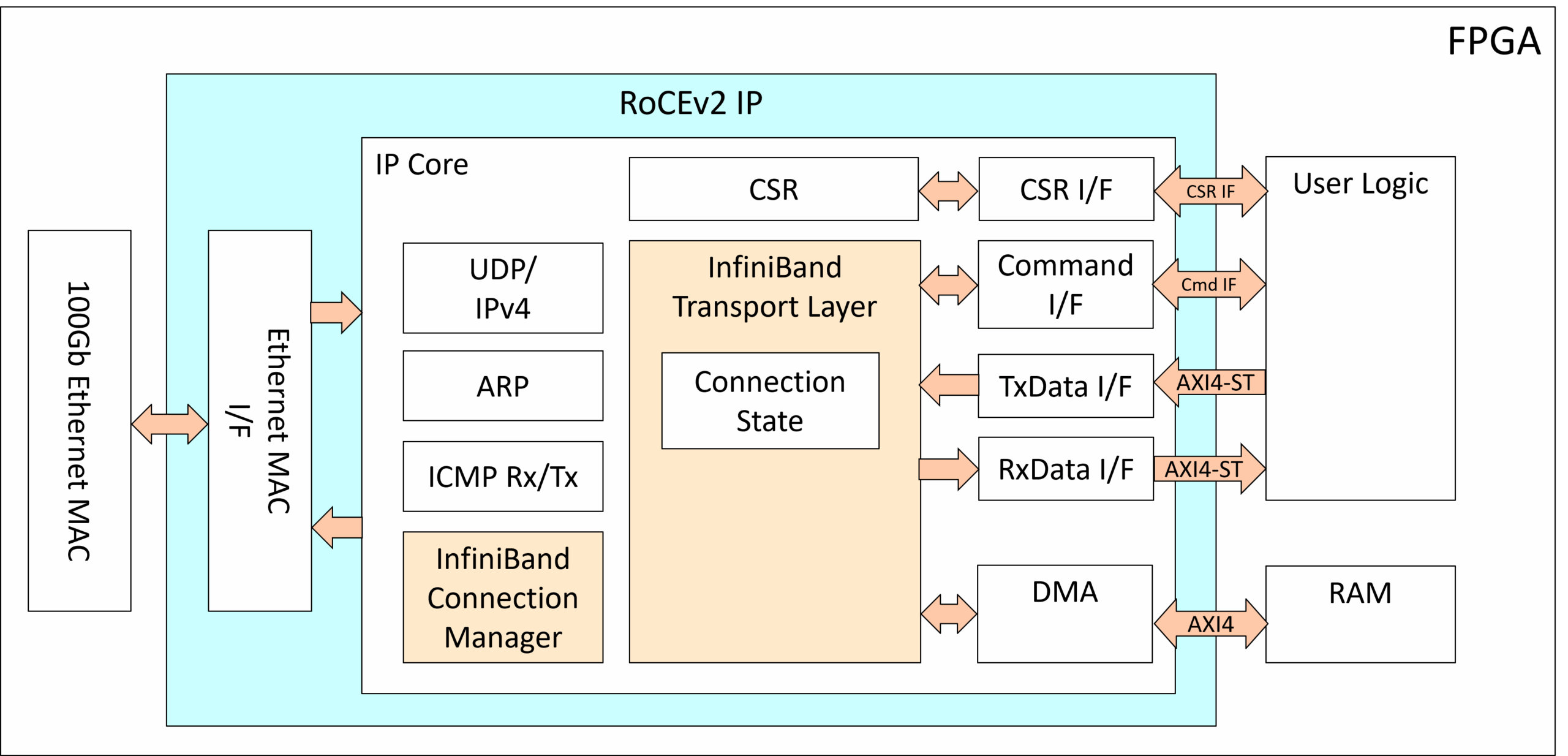

Fully hardware stack

This IP alone enables complete communication with remote nodes such as PCs, as it includes connection management functions for establishing connections, ARP for address resolution, and ping functionality for verifying connectivity.

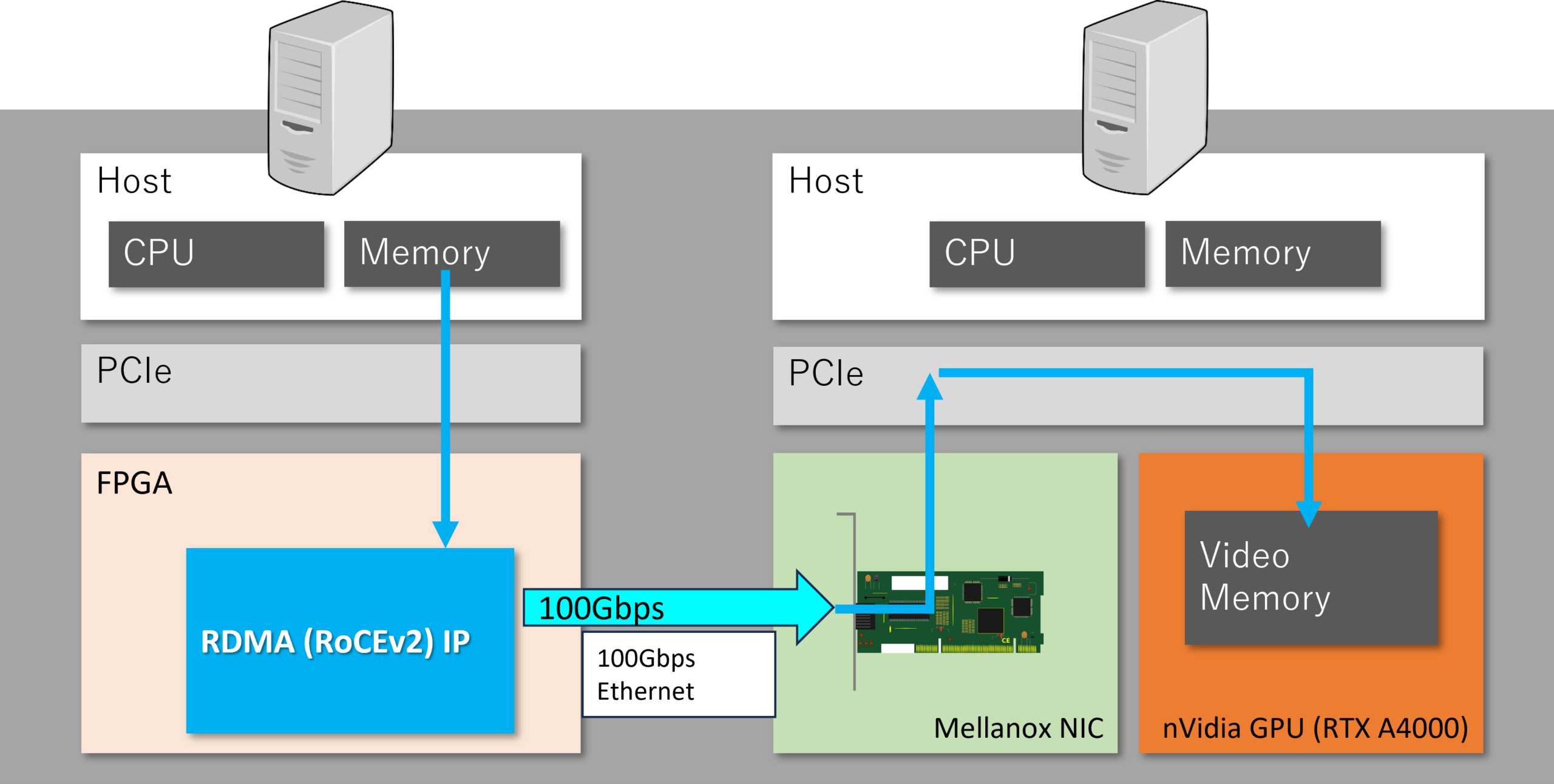

RoCEv2 IP GPU-Direct Demo

The video played on one PC is loaded onto the RoCEv2 protocol and transferred directly to the GPU memory connected to the other PC for display.

Since everything is handled in hardware, the latency is imperceptible because it’s significantly lower than the display’s refresh rate (HDMI) .

Major Specifications

| Protocol | RoCEv2, ARP, ICMP (Ping) |

| Connection Management | Utilizes “Communication Management Message” Server side functions |

| Connection Type | Reliable Connection Unreliable Connection Unreliable Datagram |

| Operations | SEND (with Immediate) RDMA WRITE (with Immediate) RDMA READ |

| Max Queue Pair | 2 – 4096 (configurable) |

| Flow Control | Supports PFC, control by VLAN/PCP tags |

| Congestion Control | Supports ECN (Explicit Congestion Notification) and rate control |

| Throughput | 100Gbps wire speed (FPGA) |

We have evaluation licenses and research licenses, please contact us.