We have extensive experience developing accelerators using PCI Express IP. We are also well-versed in technologies such as virtualization support and cache-coherent protocols, and can assist you in designing FPGA logic and driver software that utilizes these technologies.

Accelerator Development with PCI Express IP

Even when developing high-performance accelerator hardware, the architecture used by applications to utilize it often becomes the bottleneck, preventing the hardware from reaching its full potential. We can assist with development in such situations.

To leverage the performance of accelerator platforms from AMD (Xilinx) and Altera (Intel) while utilizing Vitis and OFS (Open FPGA Stack).

To improve the performance of the accelerator I wrote in HLS.

To use an accelerator written in HDL, not HLS, on AMD and Altera accelerator platforms.

To control the FPGA accelerator directly from the driver without using the accelerator platform.

Accelerator Virtual Machine Support

In recent years, server applications are increasingly running on virtual machines or containers rather than directly on physical hardware. Consequently, FPGAs must also be designed for use within virtual machines or containers.

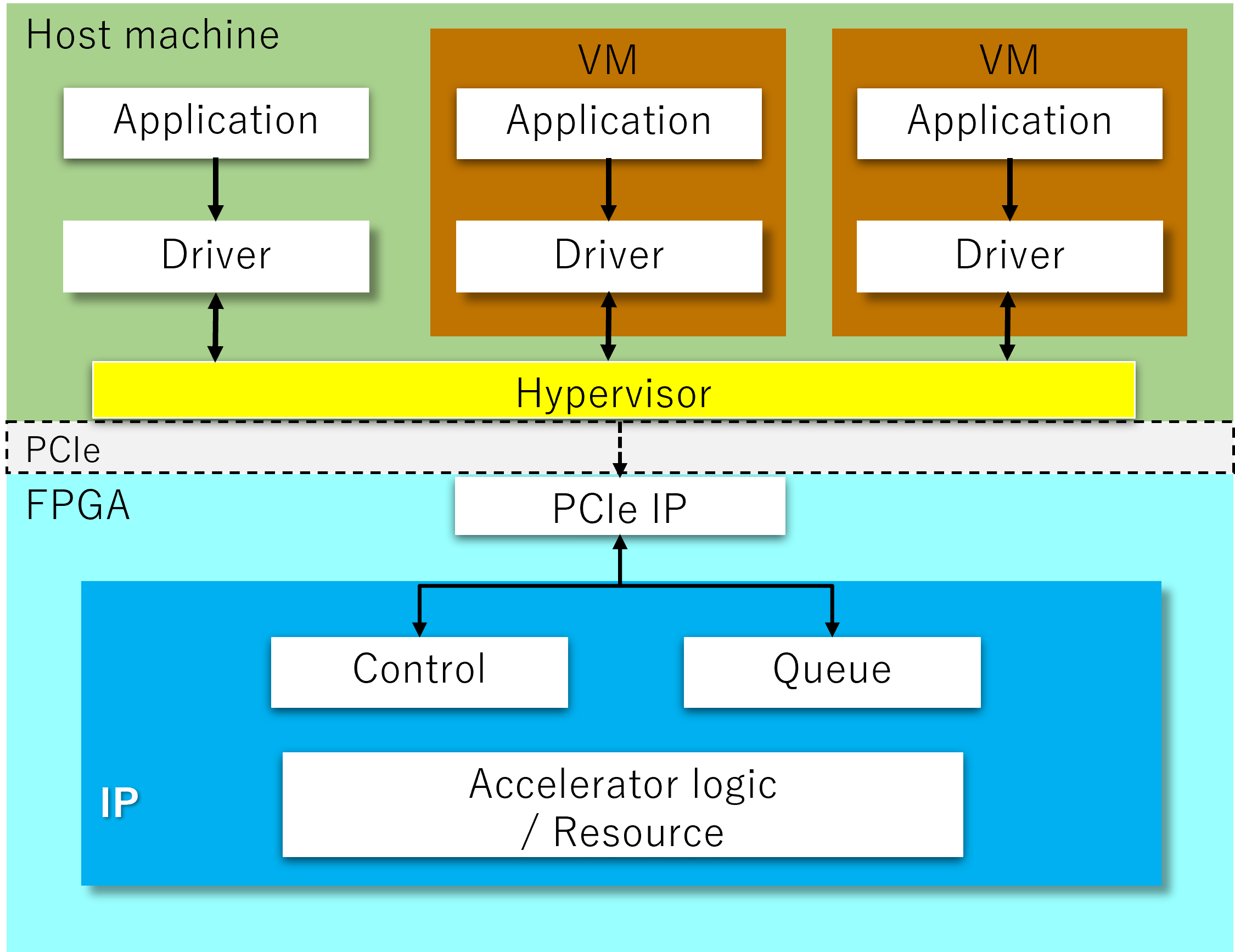

When multiple virtual machines utilize the FPGA, a hypervisor such as KVM or VirtualBox typically mediates exclusive access to the FPGA, as shown in the diagram on the right. However, this approach creates a bottleneck due to the hypervisor’s software processing.

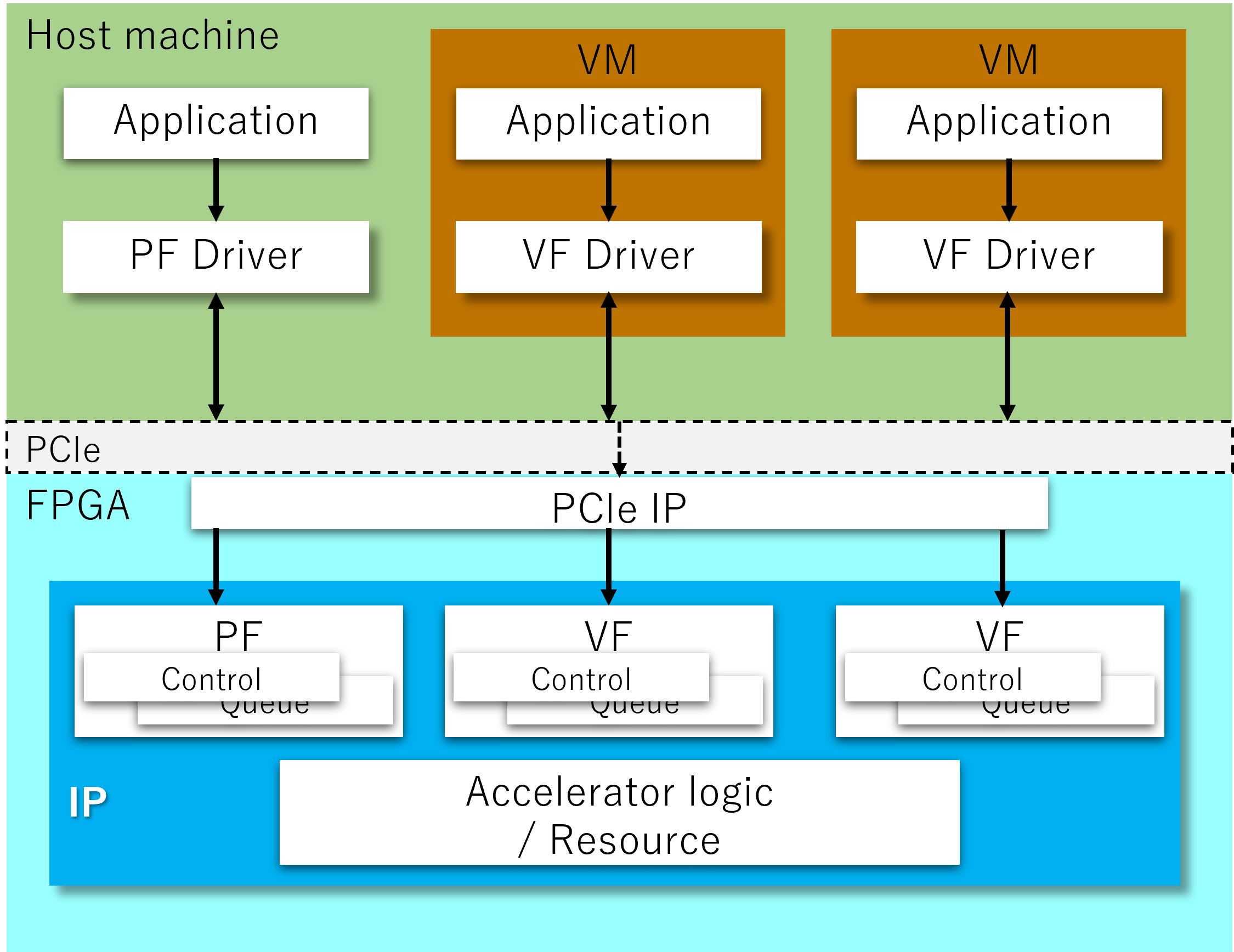

SR-IOV Support

Using the PCI Express feature SR-IOV (Single Root-IO Virtualization) enables direct device control from drivers of different VMs. Furthermore, by implementing measures such as providing isolated control registers and command queues on the FPGA side, the Hypervisor does not become a bottleneck, allowing performance equivalent to that when used directly from the physical machine.

Leveraging our expertise in developing logic optimized for SR-IOV performance and control drivers—including mastery of DMA and IOMMU—we provide support for virtual machine compatibility.