PCI Express IPを使ったアクセラレータの豊富な開発実績があります。また、仮想化対応、キャッシュコヒーレントプロトコルなどの技術に精通しており、それらを利用するFPGAロジックとドライバソフトウェアの設計をお手伝いします。

PCI express IPを使ったアクセラレータ開発

高性能なアクセラレータハードウェアを開発しても、実はアプリケーションからそれを利用するアーキテクチャがボトルネックとなって、ハードウェアの性能を発揮できないケースがほとんどです。弊社ではこのような状況の開発をお手伝いできます。

・AMD(Xilinx), Altera(Intel) のアクセラレータプラットフォーム(Vitis, OFS = Open FPGA Stack)を利用しながら性能を発揮したい

・HLSで書いたアクセラレータの性能を向上させたい

・HLSではなくHDLで書いたアクセラレータを、AMD, Alteraのアクセラレータプラットフォームで使いたい

・アクセラレータプラットフォームを利用せず、FPGAアクセラレータを直接ドライバから制御したい

アクセラレータの仮想マシン対応

近年サーバー用途では、物理マシン上で直接アプリケーションを実行するケースは少なくなっており、仮想マシンもしくはコンテナでの実行が基本となっています。そのためFPGAも仮想マシンやコンテナから利用することを想定しなくてはなりません。

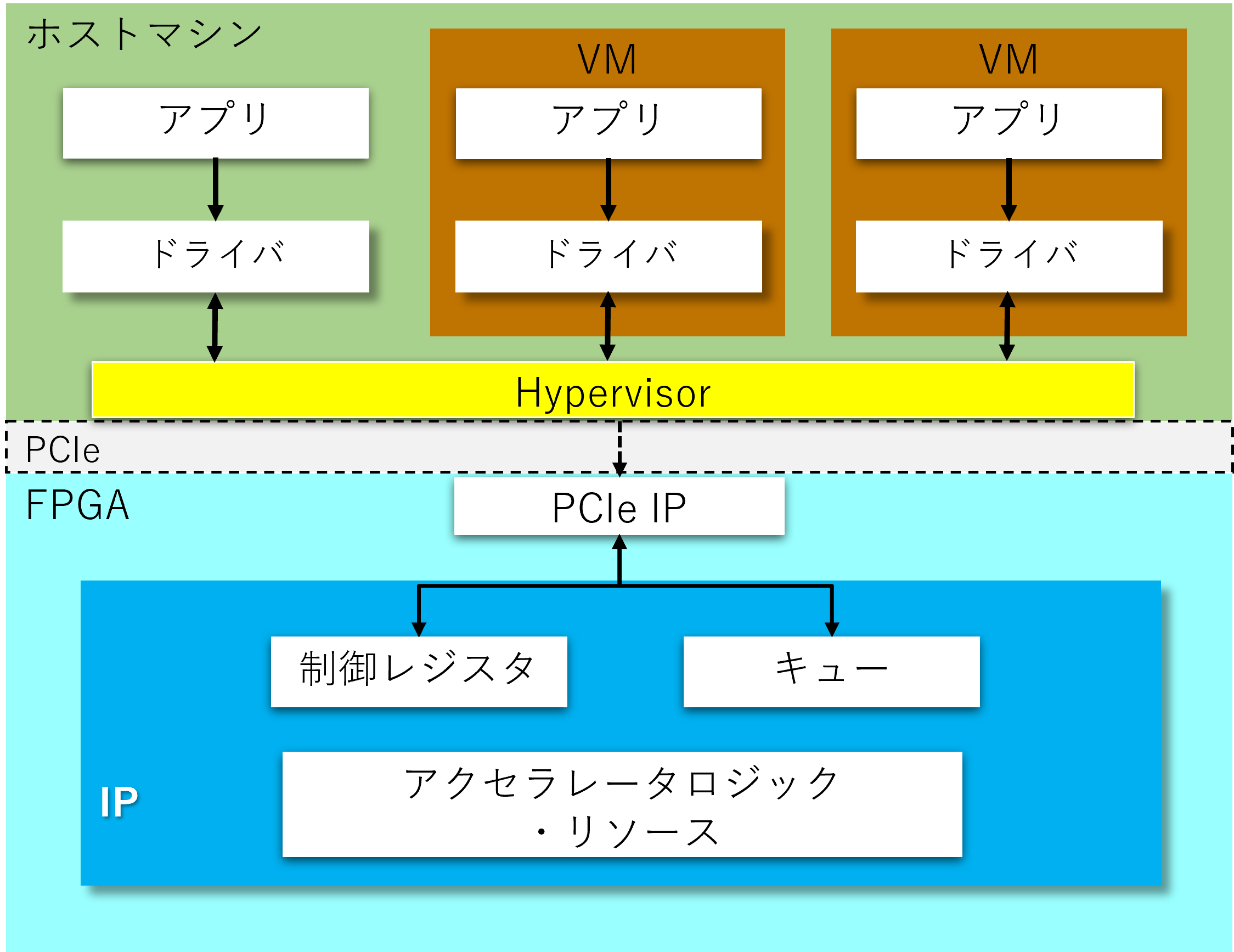

複数の仮想マシンから利用する場合、通常は右図に示すように、KVMやVirutalBoxなどを始めとするHypervisorがFPGAの排他利用を調停します。しかしこの方法だと、Hypervisorのソフトウェア処理がボトルネックとなってしまいます。

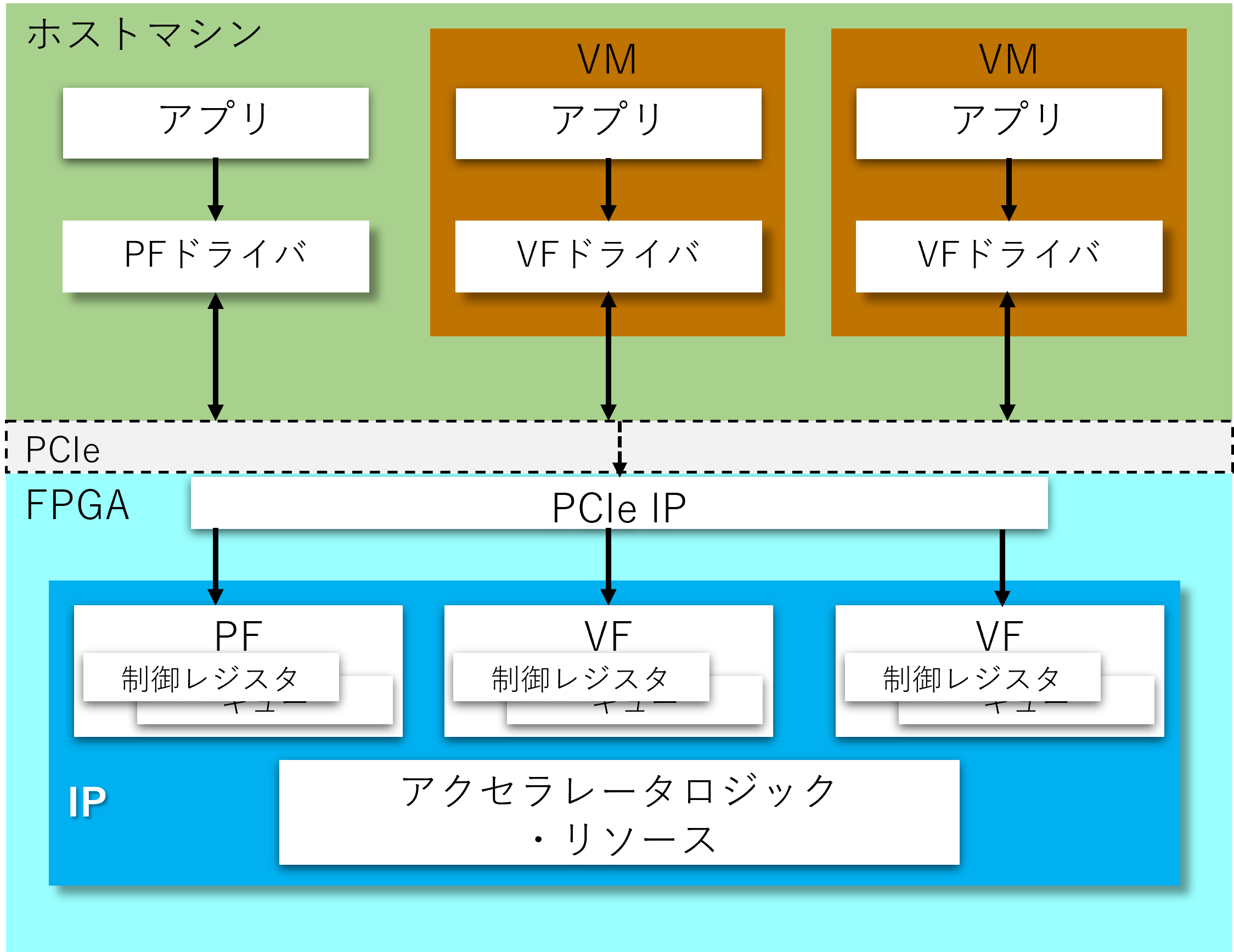

SR-IOV対応

PCI expressの機能である、SR-IOV(Single Root-IO Virtualization) の手法を使うと、異なるVMのドライバから直接デバイスを制御が可能となります。その上でFPGA側は、分離した制御レジスタやコマンドキューを用意するなど対応することで、Hypervisorがボトルネックにならず、物理マシンからの利用時と同等の性能を発揮できます。

弊社では、SR-IOVで性能を発揮するためのロジック開発や、DMAとIOMMUの使いこなしを始めとする制御ドライバ開発のノウハウを生かして、仮想マシン対応のご支援をいたします。