ハードウェアによるセキュリティ処理

ハードウェアによる高速・低遅延パケット処理エンジンを用いると、処理による遅延付加がほぼ発生しません。パケットの転送、パケットの書換え、カプセル化・カプセル解除、暗号化・復号、ロードバランサなどを実現します。

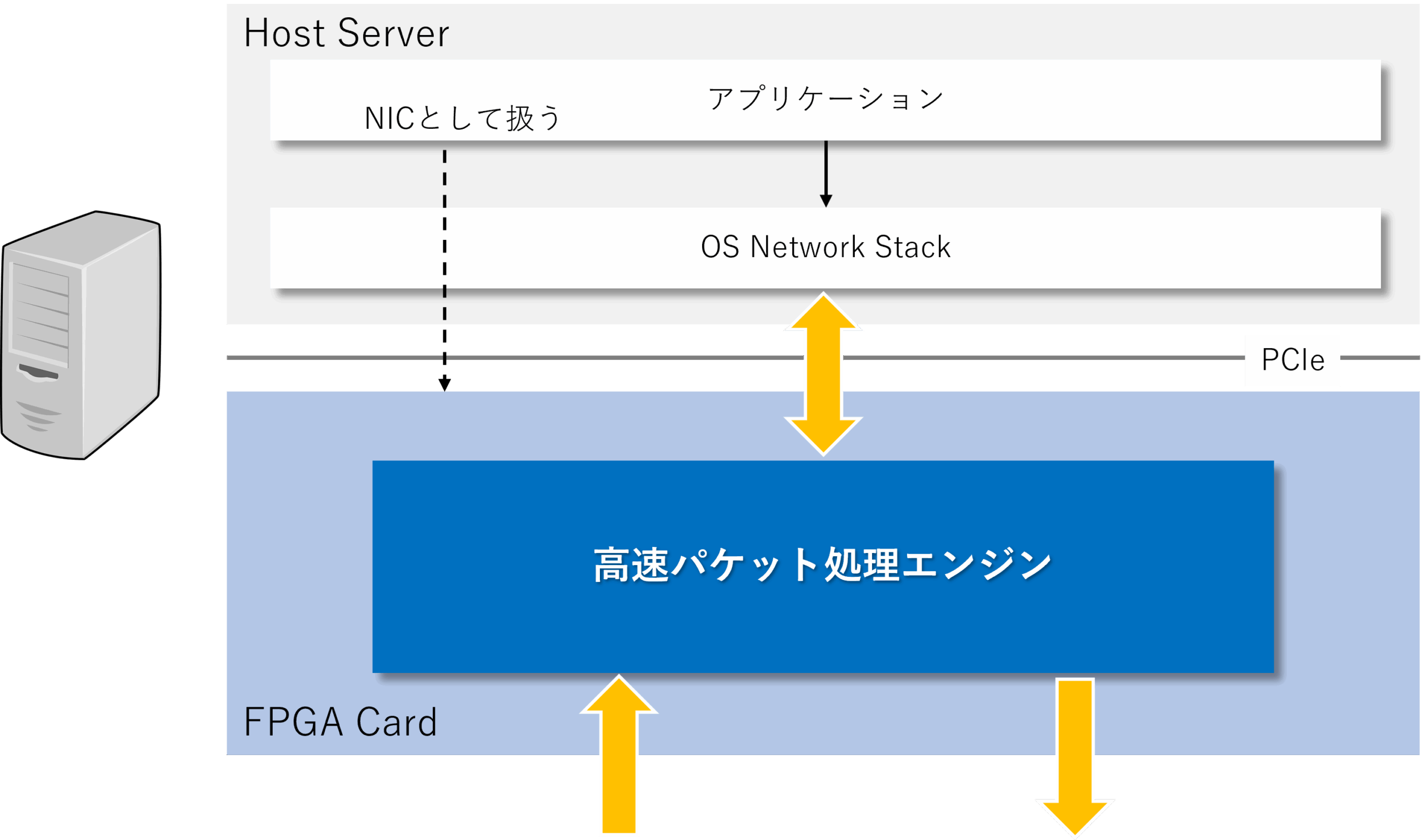

サーバのパケット処理をオフロード

サーバーに、高速イーサーネットインターフェースを持つFPGAカードを挿し、受信および送信パケットの処理をカスタムロジックを用いてオフロードします。

DDoSフィルタ、IPフィルタ、プロトコルフィルタ、DPI (Deep Packet Inspection) を用いたセキュリティフィルタや、プロトコル変換、トランスコーディング、カプセル化など、ご要望に応じた多様なパケット処理に対応可能です。基本的に1エンジンあたり100Gbpsのスループットが達成できます。また、ホストのアプリケーションからはNICとして扱うことが可能なため、従来のアプリケーションとFPGAの高速パケット処理を連携させることができます。

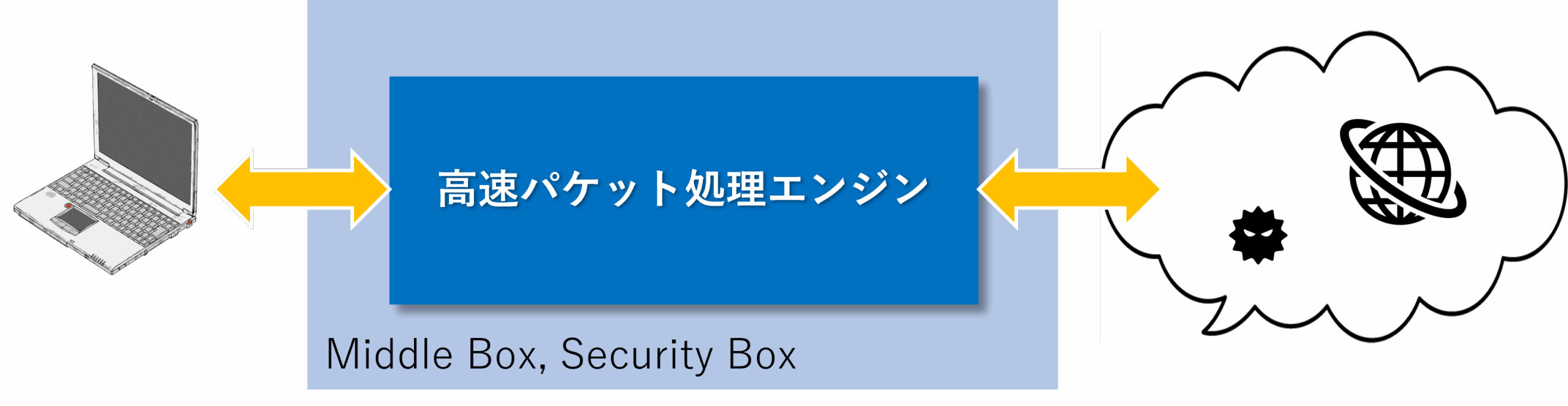

ミドルボックス・セキュリティボックス

ハードウェアによるパケット処理を、ミドルボックスの形で端末の外で処理することにより、端末におけるソフトウェア処理の負荷を増やさず、性能劣化やリソース枯渇を防ぎます。

また、ハードウェア処理固有の特徴ため、ソフトウェアのネットワークスタックで問題となる、メモリリソースに対する攻撃や脆弱性に関する攻撃の多くを無効化できるため、セキュリティを高めます。

暗号システム開発

暗号アルゴリズムのハードウェア実装を、システムに組み込む開発を承ります。暗号エンジンとネットワークプロトコルと融合させることで、超低遅延な暗号通信システムを実現、また、映像入出力と暗号エンジンを融合させることで、高スループット・低遅延なセキュアシステムを実現します。

高性能暗号実装

ハードウェアロジックでのみ可能な高並列演算アルゴリズムの実装技術により、カウンタモードやCRCのような依存のある演算も高スループットを実現

モジュール連動

PCIe連携・DMA・コヒーレント技術により、暗号ハードウェアを、ネットワークプロトコル・映像入出力・ソフトウェアと連動させ超低遅延を実現

対応暗号アルゴリズム例

| 対称鍵暗号(共通鍵暗号) | ・AES (100Gbps以上) ・AES-GCM (100Gbps以上) ・Chacha20 (100Gbps以上) ・ChaCha20-Poly1305 (100Gbps以上) など |

| 公開鍵暗号(非対称鍵暗号) | ・RSA ・ECDHE (Elliptic Curve Diffie-Hellman Ephemeral) ・PQC(ポスト量子暗号) など |

| ハッシュ関数 | ・SHA-2 (SHA-256, SHA-384) ・SHA-3 |